咸宁定制PCB制板怎么样

PCB制板设计中的ESD抑制PCB布线是ESD保护的关键要素。合理的PCB设计可以减少因故障检查和返工带来的不必要的成本。在PCB设计中,瞬态电压抑制器(TVS)二极管用于抑制ESD放电引起的直接电荷注入,因此在PCB设计中克服放电电流引起的电磁干扰(EMI)效应更为重要。本文将提供可以优化ESD保护的PCB设计标准。1.环路电流被感应到闭合的磁通变化的回路中。电流的幅度与环的面积成正比。更大的回路包含更多的磁通量,因此在回路中感应出更强的电流。因此,必须减少回路面积。很常见的环路是由电源和地形成的。如果可能,可以采用带电源和接地层的多层PCB设计。多层电路板不仅小化了电源和地之间的回路面积,还减少了ESD脉冲产生的高频EMI电磁场。如果不能使用多层电路板,则用于供电和接地的导线必须以网格形状连接。并网可以起到电源和接地层的作用。每层的印刷线路通过过孔连接,过孔连接间隔在每个方向都要在6cm以内。此外,在布线时,可以通过使电源和接地印刷电路尽量靠近来减少回路面积。PCB制板目前常见的制作工艺有哪些?咸宁定制PCB制板怎么样

不管是PCB电路板打样,还是批量生产,其制造流程和工艺步骤都差不多,只不过PCB电路板样品的成本,和批量生产前所分摊的工装费用不同。总结:制作PCB样品时,必须遵守从菲林到测试的规则。只要有一点小小的差错就会导致PCB板用处。如果需要批量生产,PCB样品必须打样。而且在打样前都要有完善的PCB加工性设计,由于缺乏简单实用的可制造性设计和分析工具,大多数工程师在设计阶段直接忽视了DFM分析过程。因此,大量的设计隐患流入生产端,终导致PCB板报废,延迟开发周期,错失产品上市时间等一系列问题。荆门高速PCB制板报价在制作双层PCB制板时有哪些注意事项?

PCB行业进入壁垒PCB进入壁垒主要包括资金壁垒、技术壁垒、客户认可壁垒、环境壁垒、行业认证壁垒、企业管理壁垒等。1客源壁垒:PCB对电子信息产品的性能和寿命至关重要。为了保证质量,大客户一般采取严格的“合格供应商认证制度”,并设定6-24个月的检验周期。只有验货后,他们才会下单购买。一旦形成长期稳定的合作关系,就不会轻易被替代,形成很高的客户认可度壁垒。2)资金壁垒:PCB产品生产的特点是技术复杂,生产流程长,制造工序多,需要PCB制造企业投入大量资金采购不同种类的生产设备,提供很好的检测设备。PCB设备大多价格昂贵,设备的单位投资都在百万元以上,所以整体投资额巨大。3)技术壁垒:PCB制造属于技术密集型,其技术壁垒体现在以下几个方面:一是PCB行业细分市场复杂,下游领域覆盖面广,产品种类繁多,定制化程度极高,要求企业具备生产各类PCB产品的能力。其次,PCB产品的制造过程中工序繁多,每个工艺参数的设定要求都非常严格,工序复杂且跨学科,要求PCB制造企业在每个工序和领域都有很强的工艺水平。

PCB布线中关键信号的处理PCB布线环境是我们在整个PCB板设计中的一个重要环境,布线几乎占到整个工作量的60%以上的工作量。布线并不是一般认为的连连看,链接上即可,一些初级工程师或小白会采用Autoroute(自动布线)功能先进行整板的连通,然后再进行修改。高级PCB工程师是不会使用自动布线的,布线一定是手动去布线的。结合生产工艺要求、阻抗要求、客户特定要求,对应布线规则设定下,布线可以分为如下关键信号布线→整板布线→ICT测试点添加→电源、地处理→等长线处理→布线优化。PCB制造工艺和技术PCB制造技术可分为单面、双面和多层印制板。

⑴信号层:主要用来放置元器件或布线。ProtelDXP通常包含30个中间层,即MidLayer1~MidLayer30,中间层用来布置信号线,顶层和底层用来放置元器件或敷铜。⑵防护层:主要用来确保电路板上不需要镀锡的地方不被镀锡,从而保证电路板运行的可靠性。其中TopPaste和BottomPaste分别为顶层阻焊层和底层阻焊层;TopSolder和BottomSolder分别为锡膏防护层和底层锡膏防护层。⑶丝印层:主要用来在电路板上印上元器件的流水号、生产编号、公司名称等。⑷内部层:主要用来作为信号布线层,ProtelDXP中包含16个内部层。⑸其他层:主要包括4种类型的层。DrillGuide(钻孔方位层):主要用于印刷电路板上钻孔的位置。Keep-OutLayer(禁止布线层):主要用于绘制电路板的电气边框。DrillDrawing(钻孔绘图层):主要用于设定钻孔形状。Multi-Layer(多层):主要用于设置多面层。PCB制板的制作流程和步骤详解。黄石定制PCB制板

PCB制板的三大类型:单面板、双面板、多层板。咸宁定制PCB制板怎么样

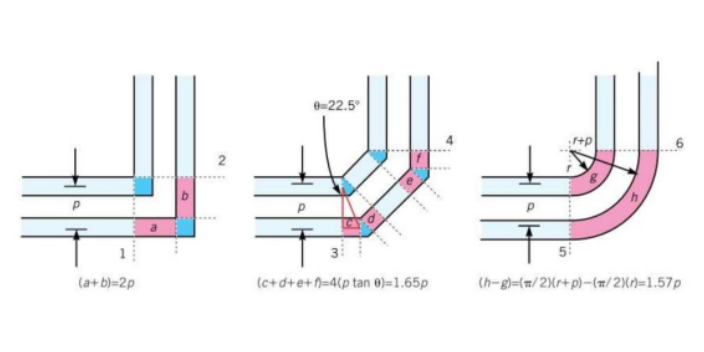

差分走线及等长注意事项1.阻抗匹配的情况下,间距越小越好2.蛇状线<圆弧转角<45度转角<90度转角(等长危害程度)蛇状线的危害比转角小一些,因此若空间许可,尽量用蛇状线代替转角,来达成等长的目的。3.圆弧转角<45度转角<90度转角(走线转角危害程度)转角所造成的相位差,以90度转角大,45度转角次之,圆滑转角小。圆滑转角所产生的共模噪声比90度转角小。4.等长优先级大于间距间距<长度差分讯号不等长,会造成逻辑判断错误,而间距不固定对逻辑判断的影响,几乎是微乎其微。而阻抗方面,间距不固定虽然会有变化,但其变化通常10%以内,只相当于一个过孔的影响。至于EMI幅射干扰的增加,与抗干扰能力的下降,可在间距变化之处,用GNDFill技巧,并多打过孔直接连到MainGND,以减少EMI幅射干扰,以及被动干扰的机会[29-30]。如前述,差分讯号重要的就是要等长,因此若无法兼顾固定间距与等长,则需以等长为优先考虑。咸宁定制PCB制板怎么样

- 恩施如何PCB设计功能 2025-06-14

- 深圳打造PCB培训原理 2025-06-14

- 黄冈打造PCB设计哪家好 2025-06-14

- 鄂州设计PCB制版功能 2025-06-14

- 黄冈定制PCB设计怎么样 2025-06-14

- 了解PCB设计原理 2025-06-14

- 高效PCB培训怎么样 2025-06-14

- 深圳高效PCB培训包括哪些 2025-06-14

- 鄂州打造PCB设计布线 2025-06-14

- 十堰如何PCB设计原理 2025-06-14

- 重庆定制变频电机 2025-06-14

- 湖北高科技机器人电机品牌 2025-06-14

- 青岛什么价格转鼓过滤器 2025-06-14

- 浙江密集型母线槽生产 2025-06-14

- 镇江常规车载录像机怎么样 2025-06-14

- 不锈钢防爆配电箱 2025-06-14

- 无锡制造电梯锁批发厂家 2025-06-14

- 国产电池模拟器2024 2025-06-14

- 四川开关电源Phoenix菲尼克斯代理供应商 2025-06-14

- 江苏医疗级UL认证变压器OEM 2025-06-14