成都6英寸管式炉BCL3扩散炉

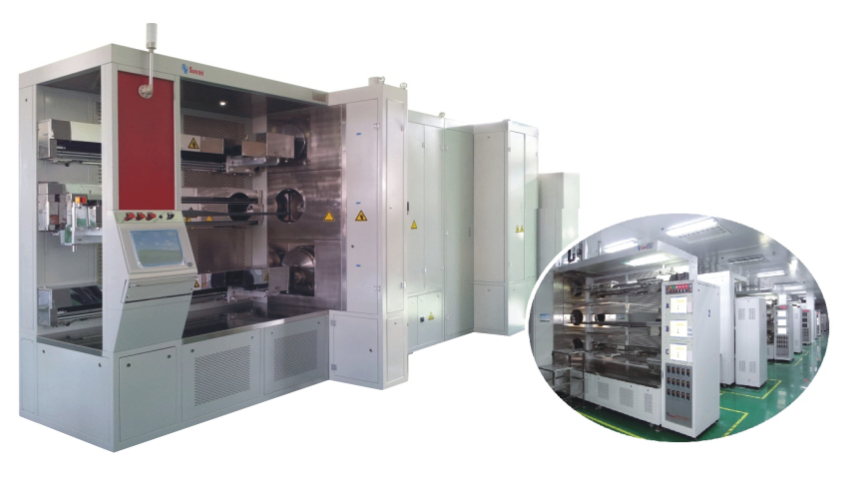

随着半导体制造向 7nm、5nm 甚至更先进制程迈进,对管式炉提出了前所未有的挑战与更高要求。在氧化扩散、薄膜沉积等关键工艺中,需实现纳米级精度控制,这意味着管式炉要具备更精确的温度控制能力、更稳定的气氛调节系统以及更高的工艺重复性,以满足先进制程对半导体材料和器件制造的严苛标准。为满足半导体工艺的发展需求,管式炉在温度控制技术上不断革新。如今,先进的管式炉配备高精度 PID 智能控温系统,结合多点温度传感器实时监测与反馈调节,能将控温精度稳定控制在 ±0.1°C 以内。在硅单晶生长过程中,如此精确的温度控制可确保硅原子有序排列,极大减少因温度偏差产生的位错、孪晶等晶格缺陷,提升晶体质量。管式炉用于金属退火、淬火、粉末烧结等热处理工艺,提升材料强度与耐腐蚀性。成都6英寸管式炉BCL3扩散炉

管式炉用于半导体衬底处理时,对衬底表面的清洁度和单终止面的可控度有着重要影响。在一些研究中,改进管式炉中衬底处理工艺后,明显提升了衬底表面单终止面的可控度与清洁度。例如在对钛酸锶(SrTiO?)、氧化镁(MgO)等衬底进行处理时,通过精心调控管式炉的温度、加热时间以及通入的气体种类和流量等参数,能够有效去除衬底表面的污染物和氧化层,使衬底表面达到原子级别的清洁程度,同时精确控制单终止面的形成。高质量的衬底处理为后续在其上进行的半导体材料外延生长等工艺提供了良好的基础,有助于生长出性能更优、缺陷更少的半导体结构,对于提升半导体器件的整体性能和稳定性意义重大。浙江一体化管式炉CVD采用先进隔热材料,减少热量损失,提升设备性能,点击咨询!

管式炉在CVD中的关键作用是为前驱体热解提供精确温度场。以TEOS(正硅酸乙酯)氧化硅沉积为例,工艺温度650℃-750℃,压力1-10Torr,TEOS流量10-50sccm,氧气流量50-200sccm。通过调节温度和气体比例,可控制薄膜的生长速率(50-200nm/min)和孔隙率(<5%),满足不同应用需求:高密度薄膜用于栅极介质,低应力薄膜用于层间绝缘。对于新型材料如二维石墨烯,管式炉CVD需在1000℃-1100℃下通入甲烷(CH?)和氢气(H?),通过控制CH?/H?流量比(1:10至1:100)实现单层或多层石墨烯生长。采用铜镍合金衬底(经1000℃退火处理)可明显提升石墨烯的平整度(RMS粗糙度<0.5nm)和晶畴尺寸(>100μm)。

管式炉在碳化硅(SiC)和氮化镓(GaN)制造中面临高温(1500℃以上)和强腐蚀气氛(如HCl)的挑战。以SiC外延为例,需采用石墨加热元件和碳化硅涂层石英管,耐受1600℃高温和HCl气体腐蚀。工艺参数为:温度1500℃-1600℃,压力50-100Torr,硅源为硅烷(SiH?),碳源为丙烷(C?H?),生长速率1-2μm/h。对于GaN基LED制造,管式炉需在1050℃下进行p型掺杂(Mg源为Cp?Mg),并通过氨气(NH?)流量控制(500-2000sccm)实现载流子浓度(101?cm?3)的精确调控。采用远程等离子体源(RPS)可将Mg***效率提升至90%以上,相比传统退火工艺明显降低能耗。管式炉通过巧妙结构设计实现高效均匀加热。

在半导体CVD工艺中,管式炉通过热分解或化学反应在衬底表面沉积薄膜。例如,生长二氧化硅(SiO?)绝缘层时,炉内通入硅烷(SiH?)和氧气,在900°C下反应生成均匀薄膜。管式炉的线性温度梯度设计可优化气体流动,减少湍流导致的膜厚不均。此外,通过调节气体流量比(如TEOS/O?),可控制薄膜的介电常数和应力。行业趋势显示,低压CVD(LPCVD)管式炉正逐步兼容更大尺寸晶圆(8英寸至12英寸),并集成原位监测模块(如激光干涉仪)以提升良率。

赛瑞达管式炉节能设计,契合半导体绿色发展,期待携手!成都6英寸管式炉BCL3扩散炉

气氛控制在半导体管式炉应用中至关重要。不同的半导体材料生长与工艺需要特定气氛环境,以防止氧化或引入杂质。管式炉支持多种气体的精确配比与流量控制,可根据工艺需求,灵活调节氢气、氮气、氩气等保护气体比例,同时能实现低至 10?3 Pa 的高真空环境。以砷化镓单晶生长为例,精确控制砷蒸汽分压与惰性保护气体流量,能有效保障晶体化学计量比稳定,避免因成分偏差导致性能劣化。管式炉的结构设计也在持续优化,以提升工艺可操作性与生产效率。卧式管状结构设计不仅便于物料的装载与取出,还能减少炉内死角,确保气体均匀流通与热量充分传递。部分管式炉集成自动化控制系统,操作人员可通过计算机界面远程监控与操作,实时查看炉内温度、气氛、压力等参数,并进行远程调节与程序设定,大幅提高了操作的便捷性与安全性。成都6英寸管式炉BCL3扩散炉

- 上海8英寸管式炉氧化扩散炉 2025-07-31

- 杭州6英寸管式炉 2025-07-31

- 北方制造管式炉氧化炉 2025-07-31

- 上海8英寸管式炉销售 2025-07-31

- 中国电科6英寸管式炉氧化炉 2025-07-31

- 浙江8吋管式炉化学气相沉积 2025-07-31

- 安徽8英寸管式炉SiN工艺 2025-07-31

- 重庆8吋管式炉SiN工艺 2025-07-31

- 广州一体化管式炉退火炉 2025-07-31

- 青岛智能管式炉氧化扩散炉 2025-07-31

- 静安区新款气缸销售厂家 2025-07-31

- 上海全自动套膜热收缩包装机源头厂家 2025-07-31

- 广西防振OPGW光缆品牌 2025-07-31

- 杭州非标定制超声波焊接技术 2025-07-31

- 高性能导电阳极丝测试系统研发 2025-07-31

- 钙钛矿电池光模拟系统厂家 2025-07-31

- 佛山过滤板成型液压机 2025-07-31

- 杭州全自动碳氢清洗采购 2025-07-31

- 浙江机械真空泵维修公司 2025-07-31

- 上海氧气体分析仪供应商 2025-07-31